摘要:烧结是低温共烧陶瓷(LTCC)基板工艺中关键工序之一,对 LTCC 基板的各项性能指标具有重要的影响。 本文以国产 MG60 生瓷带为研究对象,研究了不同烧结升温速率对 LTCC 基板介电性能、翘曲度、膜层附着力、抗折强度等性能指标的影响,分析了基板性能变化的原因。 结果表明,当升温速率为8 ℃ / min 时,基板介电常数为5. 788,介电损耗为 8. 21 × 10-4,基本无翘曲,烧结致密,附着力强,抗折强度达到 175 MPa。

关键词:低温共烧陶瓷; 升温速率; 介电性能; 翘曲度; 附着力; 抗折强度

0 引 言

低温共烧陶瓷(low temperature co-fired ceramic, LTCC)微波多层电路基板具有工作频率高、集成密度高、耐高温高湿、可集成无源元件和有利于实现微波信号耦合或隔离等独特的技术优势,被广泛应用于通信、航空航天、军事、汽车电子、医疗等领域[1-3]。 LTCC 基板是在不同层生瓷带上并行开展打孔、填孔、印刷等工艺,然后将不同层生瓷带一起叠压,最后一起烧结形成的立体互联电路基板。 烧结是 LTCC 基板工艺中关键的工序之一,它直接影响陶瓷的显微结构,进而影响陶瓷各项性能指标。 烧结过程存在复杂的物理变化和化学变化,升温速率、峰值温度和保温时间是烧结工艺中三个重要的参数,尤其是升温速率,其选择不当容易造成基板翘曲甚至开裂等问题[4-5]。

LTCC 材料从组成和结构划分可分为三类:第一类是玻璃陶瓷体系,第二类是传统意义上的玻璃-陶瓷复合体系,第三类是玻璃键合陶瓷体系[6]。 目前应用较为广泛的是第一类陶瓷,以美国 FERRO 公司开发的 A6-M 为代表,其材料是钙硅石(CaO·SiO2 ) 添加 B2O3 组成,即 Ca-B-Si-O 体系。 Wang 等[7-8] 研究了 CaO-B2O3-SiO2系 LTCC 陶瓷材料配方和制备工艺,发现玻璃添加剂可以改变陶瓷的烧结温度,调节基板的收缩率。 当CaO-B2O3-SiO2 的比例不同时,烧结温度和密度各不相同,并且介电常数和损耗也不尽相同。 增加 B2O3 的含量有助于提高机械强度,但是会恶化介电性能。 龙承毅等[9] 研究了 CaO-B2O3-SiO2 系 LTCC 基板材料的制备及烧结工艺,结果表明:在一定温度范围内,随着烧结温度的升高,基板的收缩率和密度不断增大,介电常数则先减小再增大,而抗折强度先增大后减小;当保温时间延长时,抗折强度不断减小。 目前研究以组分和烧成温度为主[10-11],而系统研究升温速率对 LTCC 基板各项性能指标影响的报道很少。

本文针对 Ca-B-Si-O 体系国产 MG60 生瓷带,采用 LTCC 工艺制作陶瓷基板,研究了烧结升温速率对LTCC 基板介电性能、翘曲度、附着力、抗折强度等关键性能指标的影响,分析了国产 LTCC 材料烧结升温速率的影响机制,为 LTCC 工艺设计提供借鉴与参考。

1 实 验

1. 1 实验流程

采用上海晶材新材料科技有限公司的生瓷带(MG60),生瓷带单层厚度为 117 μm(烧结后在 96 μm 左右)。 抗折强度测试样品层数为 30,尺寸为 40 mm × 4 mm(烧结后),介电性能、翘曲度、附着力测试样品层数为 10,尺寸为 50 mm × 50 mm(烧结后)。 验证翘曲度,表层印刷银电子浆料 MP6012,银电子浆料面积40 mm × 40 mm(烧结后);验证附着力,表层印刷可焊接电子浆料 MP6051,金属膜层面积 2 mm × 2 mm(烧结后)。 生瓷带层压力 20. 68 MPa,温度 70 ℃ ,保压时间 10 min。 采用马弗炉以 1 ℃ / min 的升温速率升温至排胶峰值温度(450 ℃ ),保温 120 min,之后分别以 4 ℃ / min、8 ℃ / min、12 ℃ / min、16 ℃ / min 的升温速率从排胶峰值温度升至烧结峰值温度(850 ℃ ),保温 15 min。

1. 2 表征方法

采用日本 JEOL 公司 JSM 5600 LV 扫描电子显微镜观察不同温度下基板微观结构;参照《电子元器件结构陶瓷材料性能测试方法》GB / T 5594. 4—2015 中介质损耗角正切值的测试方法,采用 Agilent E8363A PNA分离式介质谐振腔测试介电常数和损耗;翘曲度采用得力公司 DL9502 塞尺,放在平整的玻璃平板上测量;参照《厚膜微电子技术用贵金属浆料测试方法 附着力测定》 GB / T 17473. 4—2008,采用英国 DAGE 公司4000 系列推拉力测试仪测试附着力;参照《精细陶瓷弯曲强度试验方法》GB / T 6569—2006 中三点弯曲强度测试方法,采用深圳三思纵横公司 UTM6203 电子万能试验机测试抗折强度。 测试环境温度为(23 ± 2) ℃ ,湿度为 40% ~ 60% 。

2 结果与讨论

2. 1 升温速率对基板介电性能的影响

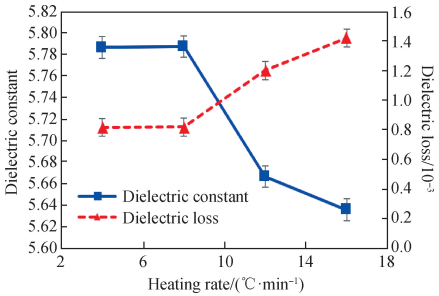

图 1 为不同升温速率烧结的陶瓷基板的介电常数(10 GHz)及介电损耗(10 GHz)。 在升温速率为4 ℃ / min时,介电常数为 5. 787,介电损耗为 8. 18 × 10-4;升温速率为 8 ℃ / min 时,介电常数为 5. 788,介电损耗为8. 21 × 10-4。 在 4 ℃ / min、8 ℃ / min 升温速率烧结的陶瓷基板介电常数、介电损耗较接近。 随着升温速率的增加,当升温速率为 12 ℃ / min 时,介电常数降至5. 667,介电损耗升至 1. 204 × 10-3;随着升温速率进一步升至16 ℃ / min,介电常数进一步降低为5. 636,介电损耗升至 1. 423 × 10-3。

图 1 不同升温速率烧结的陶瓷基板的介电常数及介电损耗

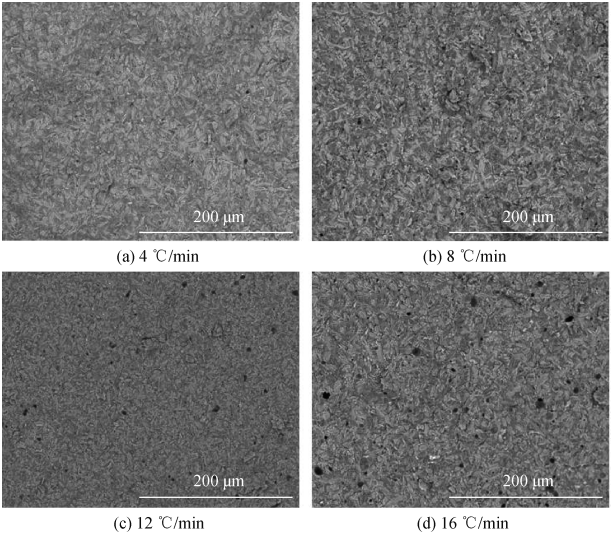

介电常数和介电损耗随升温速率的变化规律与陶瓷微观结构的变化有关。 图 2 为不同升温速率烧结的陶瓷断面的 SEM 照片, 从图 2 可 知, 升温速率由4 ℃ / min 增加至 16 ℃ / min 时陶瓷内部致密性逐渐变差,气孔率逐渐增加。 在升温速率为 4 ℃ / min、8 ℃ / min 时,烧结的样品较致密;在升温速率为 12 ℃ / min时,样品内部出现明显的气孔;在升温速率为 16 ℃ / min 时,样品断面气孔数量进一步增加。 这是因为在排胶完成后,升温速率较慢,玻璃陶瓷材料随着温度的升高,晶粒可有序生长,随着晶相的增加和晶粒的长大,内部的气孔可慢慢排出,实现玻璃陶瓷材料的致密化。 当升温速率过快时,内部的晶相未能充分析晶、长大,内部的气孔不能及时排出,导致内部气孔增多。

图 2 不同升温速率烧结的陶瓷断面的 SEM 照片

根据复合材料介电常数混合定律,低介电常数物质的引入会降低复合材料的介电常数。 由于空气的介电常数为 1,低于 CaSiO3 、CaB2O4 等晶相,因此随着升温速率增加,陶瓷基板介电常数变小,介电损耗变大。

2. 2 升温速率对基板翘曲度的影响

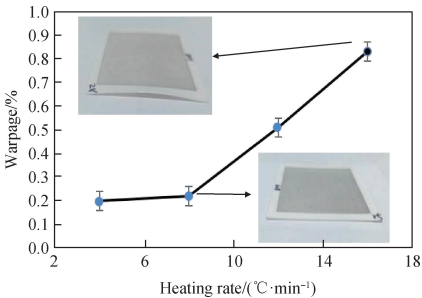

图 3 为不同升温速率烧结的基板的翘曲度和基板实物图。 由图 3 可以看出,当升温速率为 4 ℃ / min、8 ℃ / min 时,基板翘曲度为 0. 20% 左右,随着升温速率升至 12 ℃ / min、16 ℃ / min 时,基板翘曲度也在逐渐增加,在 16 ℃ / min 时,翘曲度为 0. 83% 。 从基板翘曲度实物图可以看出,升温速率为 8 ℃ / min 时基板平整性较好,16 ℃ / min 时基板中间凸起明显。 这主要是因为玻璃陶瓷材料与银电子浆料共同升温烧结,当升温速率为 4 ℃ / min、8 ℃ / min 时,银电子浆料的烧结收缩速率与玻璃陶瓷的烧结收缩速率较为接近,但是当升温速率增加至 12 ℃ / min、16 ℃ / min 时,银电子浆料的烧结收缩速率远大于玻璃陶瓷材料的烧结收缩速率[12],因此出现了烧结严重不匹配的现象,从而出现基板拱起的现象。

图 3 不同升温速率烧结的基板的翘曲度及基板照片

2. 3 升温速率对基板膜层附着力的影响

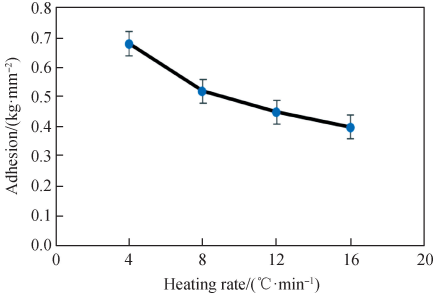

图 4 为不同升温速率烧结的膜层的附着力。 由图 4 可以看出,随着升温速率的增加,焊盘膜层附着力呈降低的趋势。 这是因为升温速率为 4 ℃ / min、8 ℃ / min 时,陶瓷烧结产生的液相较多,可以与金属膜层形成较好的附着力,同时瓷体较致密,气孔较少,金属膜层与陶瓷间的气孔少,因此结合力较高;但是当升温速率增加至 12 ℃ / min、16 ℃ / min 时,由于陶瓷烧结产生的液相含量降低,金属膜层与陶瓷间的气孔较多,降低了金属膜层与陶瓷的结合力。 由前文可知,随着升温速率的增加,金属浆料与陶瓷的共烧匹配性会变差,这也可能会导致金属膜层与陶瓷间结合力降低。

图 4 不同升温速率烧结的膜层的附着力

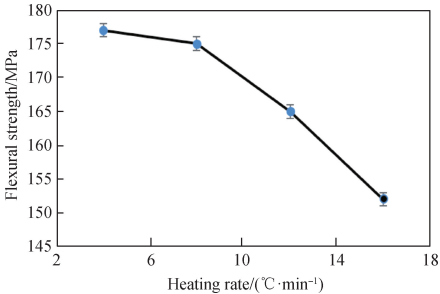

2. 4 升温速率对基板抗折强度的影响

图 5 为不同升温速率烧结的基板抗折强度趋势图。 当升温速率为 4 ℃ / min 时,陶瓷基板的抗折强度为177 MPa;当升温速率为 8 ℃ / min 时,陶瓷基板的抗折强度为 175 MPa;当升温速率为 12 ℃ / min 时,陶瓷基板的抗折强度为 165 MPa;当升温速率为 16 ℃ / min 时,陶瓷基板的抗折强度降为 152 MPa。 由图 5 可以看出,在升温速率较低时,抗折强度变化趋势不明显,但是在升温速率增加至 12 ℃ / min 时,抗折强度出现明显降低的趋势,在升温速率进一步增加至 16 ℃ / min 时,抗折强度进一步降低。 这主要是因为在升温速率为

4 ℃ / min、8 ℃ / min 时,液相产生较多,可以很好地填补陶瓷颗粒之间的缝隙,陶瓷内部较致密,陶瓷的抗冲击能力较强;在升温速率为 12 ℃ / min、16 ℃ / min 时,陶瓷内部气孔率增加,降低了陶瓷的致密度,陶瓷抗冲击能力降低,因此抗折强度降低。

图 5 不同升温速率烧结的基板的抗折强度

2. 5 升温速率的影响机制

LTCC 材料一般都是玻璃陶瓷或玻璃复合陶瓷粉的结构[6],具有较多的玻璃成分,因此 LTCC 烧结属液相烧结。 当 LTCC 材料在高温段(≥500 ℃ )时,玻璃相软化成黏性液体,将陶瓷粉粒拉近、紧贴,并使粉粒活化,在浓度差和界面张力的推动下,促使基板中气孔长大和玻璃流动,实现陶瓷体积收缩和基板致密化[13]。

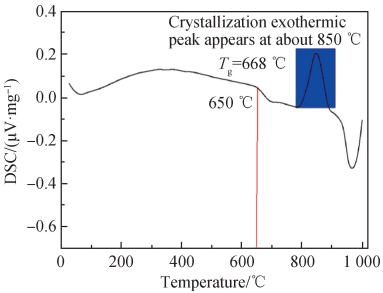

单层 LTCC 生瓷带通过流延成型,而多层生瓷带通过等静压成型形成致密的坯体。 LTCC 基板经过450 ℃的排胶峰值温度后,坯体经排胶发泡后较为疏松,其颗粒间大部分呈分开状态,颗粒间的空隙很多[14]。随着烧结温度的升高和时间的延长,特别是650 ℃后,从图 6 的陶瓷粉体的 DSC 曲线可以看出,陶瓷粉体开始吸热软化, 其玻璃化温度 ( Tg ) 为668 ℃ ,这期间陶瓷颗粒间不断发生接触和重排,大气孔逐渐消失,物质间传质过程逐渐开始进行,颗粒间接触状态由点接触逐渐扩大为面接触,固-固接触面积增加,固-气表面积相应减少。

图 6 陶瓷粉体的 DSC 曲线

随着温度不断升高,传质过程继续进行,颗粒界面不断发育长大,气孔相应缩小和变形,形成封闭的气孔。 根据 Lichteneker 混合定则,气孔的介电常数为 1,两个不同的相之间的相对介电常数符合公式(1)。

ln εm = V1ln ε1 + V2ln ε2 (1)

式中:ε1 和 ε2 分别为对应相的介电常数;εm 为两相混合后的介电常数;V1 和 V2 分别为对应相的体积分数。可以看出,气孔率增大会显著降低相对介电常数。 降低烧结升温速率能延长高温阶段时间,使得颗粒逐渐长大,气孔有足够时间迁移到颗粒界面上排出,致密度提高,介电常数提高,介电损耗降低。

烧结致密化是一个循序渐进的过程,必须在一定的温度和时间下才能完成。 当烧结升温速率加快时,收缩率曲线就会向高温方向偏移[15],物质间传质来不及完成,气孔不能及时排出,陶瓷内部的晶相不能充分析晶、长大,从而导致陶瓷内部气孔增多,密度下降,进而造成基板介电常数、介电损耗、平整度等性能指标下降。

3 结 论

(1)烧结升温速率显著影响了 LTCC 基板的微观结构。 随着烧结升温速率的提高,陶瓷基板内部气孔增多,导致基板介电常数显著降低,介电损耗增大,膜层附着力和抗冲击能力变差。 当烧结升温速率在 8 ℃ / min时,LTCC 基板不仅气孔率低,强度高,而且具有良好的介电性能。

(2)烧结升温速率会显著影响银电子浆料与玻璃陶瓷烧结收缩的匹配性。 当烧结升温速率从 4 ℃ / min升高到 16 ℃ / min 时,翘曲度从 0. 20% 提高到 0. 83% ,陶瓷基板翘曲,银电子浆料的烧结收缩速率与玻璃陶瓷的烧结收缩速率失配。

(3)LTCC 基板的烧结需要适当的升温速率,升温速率会影响烧结过程的传质、晶相长大,以及气孔排出和致密化过程,因此会影响 LICC 基板的力学和电学性能。

参考文献:略

声明:本文由 CERADIR 先进陶瓷在线平台的入驻企业/个人提供或自网络获取,文章内容仅代表作者本人,不代表本网站及 CERADIR 立场,本站不对文章内容真实性、准确性等负责,尤其不对文中产品有关功能性、效果等提供担保。本站提醒读者,文章仅供学习参考,不构成任何投资及应用建议。如需转载,请联系原作者。如涉及作品内容、版权和其它问题,请与我们联系,我们将在第一时间处理!本站拥有对此声明的最终解释权。