摘 要: 针对光电器件气密封装需求, 提出采用多层电镀技术制备含金属围坝的三维陶瓷基板。分析了该技术可行性, 重点研究了电镀时间与电流密度对镀层厚度影响, 随后采用多层图形电镀技术制备了含铜围坝的三维陶瓷基板, 最后对其围坝结构精度、结合强度及可靠性进行了测试, 并与粘接法制备的三维陶瓷基板进行对比。 结果表明, 采用多层电镀法制备的三维陶瓷基板具有围坝尺寸精度高(误差控制在10μm以内)、结合强度高(剪切强度高达45.5 MPa)、耐热性好(可耐受350 ℃高温)、腔体气密性好(漏率小于3×10-8 Pa·m³·s-1)等技术优势, 有望在光电器件(如深紫外LED、VCSEL激光器、加速度计、陀螺仪等)封装中得到应用。

关键词: 陶瓷基板; 气密封装; 电镀; 可靠性; 电子封装

随着半导体器件可靠性的不断提高, 对芯片工作环境如湿气、氧气和污染物等要求越来越高。其中,水汽含量较高会对器件和线路层造成不利影响, 一是降低器件电学性能稳定性[1], 当器件内部水汽含量高而温度较低时, 水汽会在芯片或线路层表面结霜, 进而造成器件漏电流; 二是降低器件可靠性。较高的水汽会对铝(Al)造成腐蚀, 导致电路开路[2]。器件寿命与水汽含量成负指数关系, 即随着封装体内部水汽含量的提高而迅速降低[3]。徐爱斌分别采用集成电路和分立器件进行低温耐湿老化实验, 结果表明实验至500 h 时, 集成电路累计失效达 70. 59%, 晶体管累计失效达 30. 09%[4]。此外, 若芯片或线路层上同时存在污染物时, 在水汽作用下会形成电解液, 发生电化学反应, 使芯片或线路受到腐蚀。此外, 对于某些光电器件而言, 氧气、湿气和灰尘等对其性能和寿命有很大影响。如深紫外LED发出的深紫外线会催化芯片附近的氧气形成臭氧, 降低光效, 水蒸气也会腐蚀芯片,降低器件寿命[5]; 对于激光器芯片, 发光腔面的灰尘或污染物会引起激光聚集, 导致腔面被烧毁; 对于高频晶振, 外界温度和湿度均会影响其振动频率, 增加器件不稳定性, 甚至导致停振[6]。因此, 需采用含腔体结构的三维陶瓷基板对上述光电芯片进行封装, 杜绝外界因素干扰, 为芯片提供稳定的工作环境, 从而提高器件可靠性和寿命, 如图 1 所示。

图 1 (a)深紫外 LED 气密封装结构示意图与(b)样品

目前, 市场上常见的三维陶瓷基板为低温/ 高温共烧陶瓷基板(LTCC/ HTCC), 采用丝网印刷在陶瓷胚片上制备金属线路层, 然后将多层生胚片堆叠后烧结而成。虽然 LTCC/ HTCC 基板集成度高, 耐热性好,但却存在热导率低、图形精度差、成本高等不足[7-8]。为了降低三维陶瓷基板工艺成本, 台湾阳升公司采用多层烧结法制备了 MSC( Multilayer Sintering Ceramic Substrate)基板[9], 首先制备厚膜印刷陶瓷基板, 随后通过丝网印刷将陶瓷浆料印刷于厚膜陶瓷基板上形成单层围坝结构, 在低温下(100 ~ 200 ℃, 1 h 以上) 进行干燥形成围坝胚层; 随后在胚层上继续印刷陶瓷浆料并固化, 直到围坝胚体厚度达到要求, 最后通过高温烧结成型。 与 HTCC/ LTCC 相比, MSC 基板制备技术和工艺简单, 平面基板与围坝结构独立烧结成型,成本较低。此外, 由于围坝与平面基板均为陶瓷材料,热膨胀系数匹配, 制备与使用过程中不会出现基板翘曲和脱层等现象, 且围坝经高温烧结制备, 与底部结合强度及自身强度较高。其缺点在于, 下部陶瓷基板线路层与上部围坝结构均采用丝网印刷布线, 图形精度较低; 同时因受丝网印刷工艺限制, 所制备的 MSC 基板围坝厚度( 高度) 有限。因此 MSC 三维陶瓷基板仅适用于体积较小、精度要求较低的电子器件封装。为了提高三维陶瓷基板围坝精度, 台湾某公司提出采用胶粘法制备 DAC ( Direct Adhesive Ceramic Substrate) 三维陶瓷基板[10], 首先加工金属环和 DPC 陶瓷基板, 然后通过粘接剂将两者对准贴合并在低热条件下固化, 实现金属环与 DPC 基板粘接。粘接法具有工艺简单、成本低廉和易于批量生产等优势, 且制备工艺温度低, 不会对 DPC 基板线路层造成损伤。然而, 由于有机粘胶耐热性差, 且为非气密性材料, 因此可靠性较低。

综上所述, 目前三维陶瓷基板难以满足精度、成本及可靠性的应用需求, 亟需开发新型的三维陶瓷基板制备技术。电镀陶瓷基板(DPC)是近年来研发的一种新型陶瓷电路板, 具有导热/ 耐热性好、图形精度高、可垂直互连等技术优势, 广泛应用于半导体照明(白光 LED)、杀菌消毒(深紫外 LED)和高温电子器件封装[11]。考虑到 DPC 陶瓷基板金属线路层采用电镀工艺制备, 由于金属镀层厚度与电流密度和电镀时间成正比, 通过增加电流密度, 延长电镀时间, 可以制备出厚度较大的金属围坝层, 从而制备出具有腔体结构的三维陶瓷基板。有鉴于此, 本文提出采用多层电镀技术制备含金属围坝的三维陶瓷基板(3DPC), 研究了其技术可行性及工艺条件对基板性能的影响。

1 理论分析与实验

1. 1 理论分析

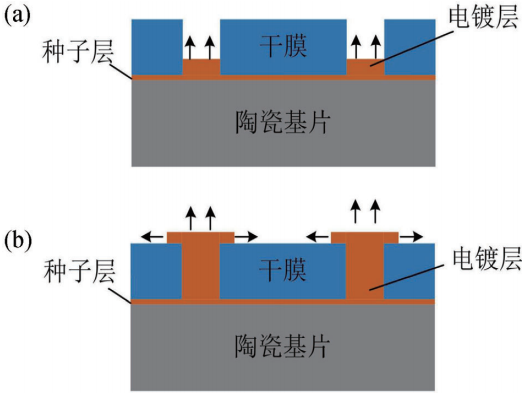

图 2 为 DPC 陶瓷基板制备过程中图形电镀生长示意图。 电镀开始时, 铜原子沉积于金属种子层表面,镀层沿着干膜厚度方向生长(如图 2(a)所示); 电镀一段时间后, 镀层厚度超过干膜厚度, 镀层沿着干膜表面生长(如图 2(b)所示), 这将导致线路层图案变形,甚至引起短路。此外, 由于干膜被镀铜层覆盖, 在后续退膜时难以完全被刻蚀液去除。因此, 干膜厚度被视为单次电镀铜层最大厚度。一般而言, 为了满足器件气密封装需求, 腔体深度(围坝厚度)要求大于 500μm。考虑到市场上干膜厚度有限(一般为 40, 50 和 75μm), 且厚干膜对曝光机也提出了更高需求, 本研究提出采用多层图形电镀(贴干膜、曝光、显影、电镀增厚, 然后重复) 提高围坝厚度, 制备出具有腔体结构的三维陶瓷基板。

图 2 镀层生长方向(a)干膜厚度和(b)干膜表面

电镀过程中, 阴极沉积铜的质量遵守法拉第电解定律。具体而言, 阴极上沉积铜和阳极上溶解铜的质量与通过电镀体系的电量成正比, 如式(1)所示[12]。

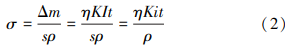

式中: 电流效率 η = 0. 95; Δm 为通过电镀沉积在阴极或阳极消耗的铜质量; 电化学当量 K= 1. 186 g·A-1·h-1; Q 为通过电镀系统的电量; I 为电镀电流; t 为电镀时间。根据式(1)可推算出电镀铜层厚度(σ), 如式(2)所示。

式中: s 为阴极镀层面积; i 为电流密度, 即单位阴极面积上电流大小, 铜密度 ρ = 8.9 g·cm-3。将上述值代入式(2) 并归一化后, 得式( 3), 电镀时间 t 由式(4)计算得到。

由式(3)和(4)可以看出, 电流密度和电镀时间是影响镀层厚度的主要因素。 由前述分析可知, 单次镀层厚度 σ 还受制于曝光机能力(实验所用曝光机最大干膜曝光厚度为 150 μm)。 为了提高制备效率, 在陶瓷基板上一次贴两层 75 μm 干膜(总厚度约 150 μm),随后进行曝光; 为了防止镀铜层过厚而盖住干膜, 实际控制单次电镀厚度 σ 为 120 μm。此外, 考虑到电流密度越大, 电镀时间越短, 生产效率越高, 但过高的电流密度会导致镀层内应力增加, 从而导致陶瓷基板翘曲。研究表明[13], 镀层内应力随电流密度的增加先降低后升高( 如图 3 所示), 当电流密度为 1.5 A·dm-2时, 镀层内应力最小。因此, 实验选用电流密度 i 为 1.5 A·dm-2。将上述数值代入式(4), 得到电镀时间 t = 363. 6 min。为便于计时, 本实验中单次电镀时间选取为 360 min。

图 3 电镀层内应力与电流密度关系

1. 2 三维陶瓷基板制备

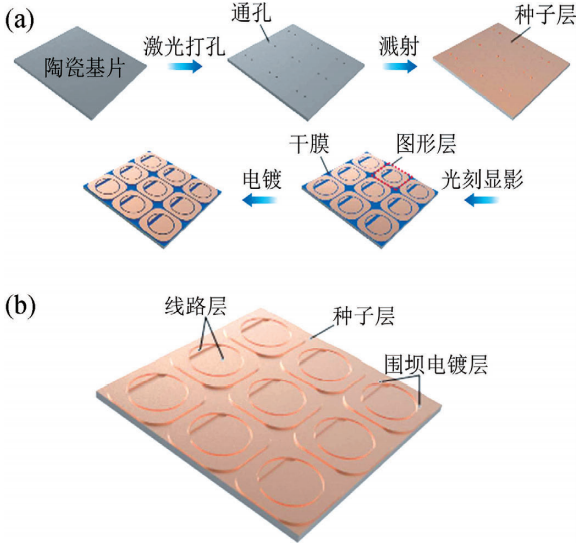

实验首先制备平面 DPC 陶瓷基板, 其工艺流程如图 4( a) 所示。 采用激光在陶瓷基片( 96% Al2O3)上打孔, 超声清洗后通过溅射镀膜制备种子层( Ti/Cu) , 然后贴干膜、光刻、显影得到金属线路层, 最后通过电镀填孔及增加线路层厚度。与制备平面DPC基板不同, 接下来只需去除表面干膜, 并不需要刻蚀种子层( 便于后续电镀生长铜围坝) , 如图4(b)所示, 其外围环形结构为电镀围坝层, 内部圆形图案是线路层。

图 4 (a)DPC 陶瓷基板制备工艺流程图; (b)DPC陶瓷基板示意图

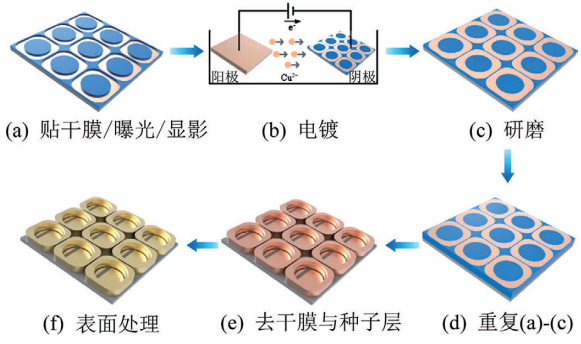

接下来采用多层图形电镀技术增厚铜围坝, 制备三维陶瓷基板[14], 如图 5 所示。具体工艺包括: (1)在上述 DPC 陶瓷基板上贴干膜(两层), 然后曝光、显影, 露出环形围坝层; (2)电镀增厚围坝层; (3)表面研磨, 提高电镀铜层厚度均匀性; (4)重复上述(1)-(3)工序, 获得具有一定厚度的镀铜围坝; (5)去除干膜和金属种子层; (6) 表面处理采用化学镀银或镍金层, 提高陶瓷基板表面可焊性及抗氧化能力。

2 结果与讨论

2. 1 基板形貌与尺寸精度

按照上述工艺制备的三维陶瓷基板(3DPC)如图 6(a)所示。整个陶瓷基板上可一次性制备多个三维陶瓷基板单元, 每个单元(尺寸为 3.5 mm×3.5 mm) 相互独立, 沿着陶瓷基片长度和宽度方向排列。图 6( b)为三维陶瓷基板截面图, 从图中可以看出, 上层围坝由多层(多次)电镀铜组成(厚度为 700 μm 的铜围坝,需要经过 6 次电镀; 此外, 为便于后续封装时固定石英玻璃片, 还特地制备了台阶结构)。研究过程中,由于三维陶瓷基板为三明治结构(铜层-陶瓷-铜层),且上层电镀铜围坝厚度较大(一般大于 500 μm), 为防止铜-陶瓷热膨胀系数不匹配导致的基板翘曲, 同时在陶瓷基片反面制备了电镀铜层。

图 5 含镀铜围坝的三维陶瓷基板(3DPC)制备工艺流程图

图 6 含镀铜围坝三维陶瓷基板(a)多阵列单元和(b)横截面图

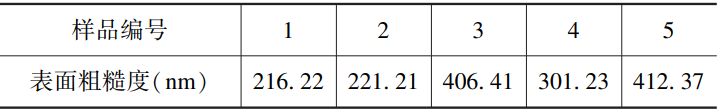

在光电器件封装过程中, 一般使用焊接或粘接方法实现上部盖板与下部基座(三维陶瓷基板)间固定。考虑到围坝表面粗糙度会对焊接/ 粘接性能造成一定影响, 实验采用表面轮廓仪对围坝表面粗糙度进行了测量, 结果如表 1 所示。由结果可知, 围坝表面粗糙度平均值为 311. 49 nm, 一定的粗糙度对熔融焊料或粘接剂有毛细吸附作用, 促进焊接/ 粘接层的润湿铺展,从而提升封装质量。

表 1 围坝表面粗糙度测量结果

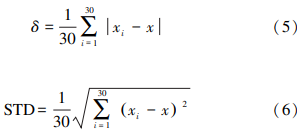

为了分析三维陶瓷基板围坝结构精度, 在整板上随机选取 20 个三维陶瓷基板单元, 采用激光共聚焦显微镜测量围坝深度、直径和间距。其中, 围坝深度、直径和间距设计值分别为 700, 2550 和 3500 μm, 其平均差 δ 与标准差 STD 按式(5)和(6)计算。其中, x为围坝深度、 直径和间距设计值, xi为实际测量值。

图 7 为制备的三维陶瓷基板围坝结构精度测试结果。由图中可知, 围坝(腔体)深度、直径和间距误差平均值分别为 4.40, 4. 6 和 7.93 μm。一般而言, 芯片贴装精度允许误差范围为±25 μm[15], 因此三维陶瓷基板围坝精度在允许误差范围内。此外, 围坝深度、直径和间距标准差分别为 5. 16, 5. 58 和 9. 18 μm, 均小于 10 μm, 样品实测值都集中分布在设计值附近,三维陶瓷基板尺寸精度可满足封装应用要求。 这主要是因为镀铜围坝的轮廓及位置精度主要由光刻工艺决定, 而每次电镀完成后, 还需要对基板表面进行研磨,提高厚度均匀性, 因此, 采用多层电镀法制备的三维陶瓷基板精度较高。

图 7 含镀铜围坝的三维陶瓷基板结构尺寸精度

2. 2 基板可靠性分析

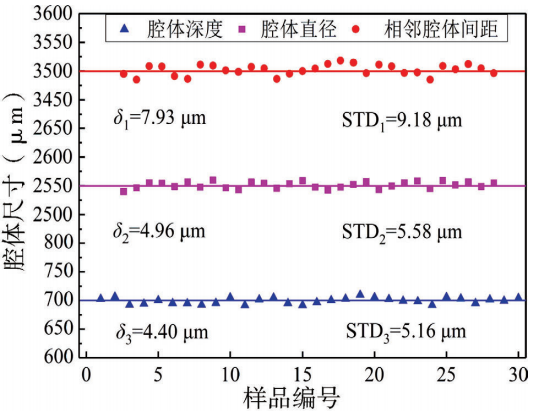

为了评价三维陶瓷基板可靠性, 实验采用多功能推拉力测试仪(DAGE-4000 Plus), 测试高温烘烤前后三维陶瓷基板电镀铜围坝与下部 DPC 基板间的剪切强度, 并与采用环氧粘接法制备的三维陶瓷基板进行对比。图 8 为两种三维陶瓷基板剪切强度测试结果。由图 8(a)可知, 多层电镀法制备的三维陶瓷基板剪切强度为 45. 5 MPa, 采用粘接法制备的三维陶瓷基板剪切强度仅为 2.1 MPa; 经高温烘烤(24 h@ 350 ℃)后, 前者强度降至 41.3 MPa(下降 9.2%), 这主要是由于金属铜与氧化铝陶瓷间热膨胀系数不匹配造成的, 而后者剪切强度上升了 28.6%, 推测原因是高温促进了环氧胶固化。但粘接法制备的三维陶瓷基板在高温烘烤后, 粘接胶外溢到线路层上, 会对封装过程及器件性能造成不利影响, 如图 8(b)所示。

图 8 (a)两种三维陶瓷基板高温烘烤前后剪切强度;(b)高温烘烤后粘接法制备三维陶瓷基板样品图

最后采用氦质谱仪对三维陶瓷基板气密性进行了测试, 结果如表 2 所示。采用多层电镀法制备的五组三维陶瓷基板样品气漏率均低于3×10-8Pa·m3·s-1(平均值为1.7×10-8Pa·m3·s-1), 具有良好气密性,满足光电器件气密封装需求。

综上所述, 采用多层电镀法制备的三维陶瓷基板具有较高的图形精度、围坝结合强度以及可靠性(含气密性), 可满足高精度、高可靠器件气密封装需求,具有较大的市场潜力。

表 2 多层电镀三维陶瓷基板气密性检测结果

3 结论

为满足光电器件气密封装需求, 在电镀陶瓷基板(DPC)基础上, 提出采用多层电镀技术制备含金属围坝的三维陶瓷基板。 分析和验证了该技术可行性, 并研究了电镀工艺对三维陶瓷基板性能的影响。 结果表明, 采用多层电镀法制备的三维陶瓷基板, 电镀铜围坝尺寸精度高(误差控制在 10 μm 以内), 结合强度大(常温下高达 45. 5 MPa), 耐热性好(经 350 ℃ 烘烤 24h 后结合强度仍高于 40 MPa), 腔体气密性好(一般为10-8Pa·m3 ·s-1量级), 有望在光电器件( 如深紫外LED、VCSEL 激光器、加速度计、陀螺仪等) 封装中得到应用。

参考文献:

[1] Han B, Kim D. Moisture ingress, behavior and prediction inside semiconductor packaging: a review [J]. Journal of Electronic Packaging, 2017, 139: 010802.

[2] 张秀霞. 半导体器件和集成电路水汽含量控制的研究 [J]. 电子工业专用设备, 2009, 38(4): 48-50.

[3] 贾松良. 封装内水汽含量的影响及控制 [J]. 电子与封装, 2002,2(6): 12-14.

[4] 徐爱斌. 内部水汽对半导体器件可靠性影响的研究 [J]. 电子产品可靠性与环境试验, 1994(2): 49-54.

[5] Muramoto Y, Kimura M, Nouda S. Development and future of ultraviolet light-emitting diodes: UV-LED will replace the UV lamp [J]. Semiconductor Science and Technology, 2014, 29 (8): 84004-84011.

[6] Wang S, Xie G, Su Y, et al. Reduced graphene oxide-polyethylene oxide composite films for humidity sensing via quartz crystal microbalance [J]. Sensors and Actuators B: Chemical, 2018, 255(2): 2203-2210.

[7] 吕安国, 谢廉忠, 周勤. MCM 多层共烧陶瓷基板技术研究进展[J]. 混合微电子技术, 2010, 21(1): 35-40.

[8] 崔嵩, 黄岸兵, 张浩. MCM 用氮化铝共烧多层陶瓷基板研究[J]. 电子元件与材料, 2003, 22(8): 25-28.

[9] 庄弘毅, 曾国书, 蒋诚光. 具有网版印刷环绕壁的 LED 装置:CN204102938U [P]. 2015-01-14.

[10] 章军, 罗素扑, 唐莉萍, 等. 一种紫外 LED 封装用的围坝陶瓷基板制备方法: CN106531865B [P]. 2019-06-21.

[11] 程浩, 罗小兵, 彭洋, 等. 电子封装陶瓷电路板 [J]. 现代技术陶瓷, 2019, 40(4): 265-292.

[12] 李明刚. GaN 垂直结构 LED 电镀铜衬底的研究 [D]. 长春: 长春理工大学, 2008.

[13] Basrour S, Robert L. X - ray characterization of residual stresses in electroplated nickel used in LIGA technique [J]. Materials Science and Engineering A, 2000, 288(2): 270-274.

[14] Hao C, Yun M, Yang P, et al. White LEDs with high optical consistency packaged using 3D ceramic substrate [J]. IEEE Photonics Technology Letters, 2019, 31(22): 1818-1821.

[15] Wu T, Lou Y, Wu F, et al. Study on correction method for die position deviation caused by adhesive tape puncture [J]. IEEE Transactions on Components, Packaging and Manufacturing Technology, 2018, 9(7): 1388-1395.

声明:本文由 CERADIR 先进陶瓷在线平台的入驻企业/个人提供或自网络获取,文章内容仅代表作者本人,不代表本网站及 CERADIR 立场,本站不对文章内容真实性、准确性等负责,尤其不对文中产品有关功能性、效果等提供担保。本站提醒读者,文章仅供学习参考,不构成任何投资及应用建议。如需转载,请联系原作者。如涉及作品内容、版权和其它问题,请与我们联系,我们将在第一时间处理!本站拥有对此声明的最终解释权。